吴忠仪表宁光电表有限公司 (宁夏银川750011) 李建炜

关键词:CS5460A,电能表,串行接口,计量

1 引 言

CS5460A是美国CRYSTAL公司最新推出的带有串行接口的单相双向功率/电能计量集成电路芯片,现主要应用在单相电子式电能表和三相电子式电能表中。该芯片的性能优于其它计量芯片,主要表现在:

·可测量瞬时电流、瞬时电压、瞬时功率、电流有效值、电压有效值、功率有效值和电能计量;

·具有片内看门狗定时器(Watch Dog Timer)与内部电源监视器;

·双向串行接口与内部寄存器阵列可以方便地与微处理器相连接;

·具有机械计度器/步进马达驱动器;

·片内2.5V参考电压;

·外部时钟最高频率可达20MHz;

·具有功率方向输出指示;

·提供了外部复位引脚。

2 技术特性

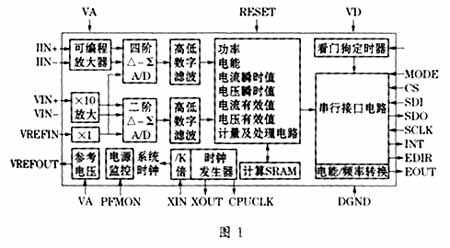

CS5460A是一个包含两个△Σ模-数转换器(ADC)、一个串行接口的具有高速电能计量功能的高度集成△Σ模-数转换器。CS5460A具有与微控制器通讯的双向串口和与能量成正比的频率可编程的脉冲输出。CS5460具有方便的片上AC/DC系统校准功能。CS5460A能独自工作,在系统上电后自动初始化。芯片内结构见图1,引脚功能如下:

1脚XOUT:晶体振荡器输出。

24脚XIN:晶体振荡器输入。XOUT,XIN——芯片内的一个门电路与这些引脚相连,可连接晶体为芯片提供系统时钟。另外,也可以有外部时钟(与CMOS时钟兼容)驱动引脚XIN,为芯片提供系统时钟。

2脚CPUCLK:CPU时钟输出。CPUCLK——片上振荡器的输出,可以驱动一个标准的CMOS负荷。

3脚VD+:数字电路电源正极。以DGND为参考,一般为+5V±10%。

4脚DGND:数字地。数字接地,与VA-具有相同的电平。

5脚SCLK:串行时钟输入。该脚确定SDI和SDO引脚的输入和输出速率。此输入具有一个允许使用边沿缓慢的信号的施密特触发器。只有当CS低时,SCLK引脚才识别时钟。

6脚SDO:串行数据输出。SDO是串行数据端口的输出引脚,当CS高时,其输出将处于高阻抗状态。

7脚CS:片选。当处于低电平时,端口可以识别SCLK。该脚高电平状态使SDO引脚处于高阻抗状态。CS应在SCLK处于低电平时改变状态。

8脚MODE:模式选择。当处于高电平时CS5460A开始执行自导入序列,从外接EEPROM读取命令和设置。当处于低电平时CS5460运行在常规命令模式。引脚不连接时下拉为逻辑低电平。

9脚VIN+:差分电压正输入端。

10脚VIN-:差分电压负输入端。VIN+、VIN-—电压通道的差分模拟输入引脚。

11脚VREFOUT:参考电压输出。芯片上的参考电压由该引脚输出,参考电压的标称值为2.5V(以VA-引脚为参考)。

12脚VREFIN:参考电压输入。该引脚输入的电压给芯片上的调制器提供参考电压。

13脚VA-:模拟地负极。负模拟电源引脚,必须具有最低的电压。

14脚VA+:模拟电源正极。以VA-为参考,通常为+5V±10%。

15脚IIN-:差分电流负输入端。

16脚IIN+:差分电流正输入端。IIN-、IIN+为电流通道的差分模拟输入引脚。

17脚PFMON:电源掉电监视输出。PFMON——掉电监视器,用来监视模拟电源,相对于VA-引脚的典型阀值电平为2.5V,具有+/-50mV的滞环。如果PFMON的电压低于阀值,则状态寄存器的LSD(低电源检测)位将被置位。

18脚NC:空脚。该引脚保持悬浮态。

19脚RESET:复位输入。RESET——当复位引脚为低电平时,所有内部寄存器都被设置为缺省值。

20脚INT:中断输出。当INT变低时,表明一个允许的事件已发生。可以通过向CS5460A写入适当命令来使INT清除(逻辑1)。

21脚EOUT:电能脉冲输出。EOUT——电量输出引脚,输出一个脉冲宽固定、频率(可编程)和电能成比例的脉冲串。

22脚EDIR:能量方向指示输出。如果测量到的电能是负值,电能方向指示器发出指示。

23脚SDI:串行数据输入。SDI是串行数据接口的输入引脚。数据的输入速率由SCLK决定。

3 操作原理

CS5460A可以在单一+5V电源下运行。电流通道输入范围为30mVRMS或150 mVRMS,电压通道输入范围为150 mVRMS。当在VA+/-引脚用单电源+5V供电时,CS5460A可以承受范围为-0.25V到VA+的共模信号。总功耗<500mW;电能计量精度:在1000∶1动态范围以上每秒读取0.1%;电流测量精度:读数的0.1%;瞬时功率测量精度:读数的0.1%。供电引脚最大输入电流为±50mA;(VA+)-(VA-)≤+6.0V。

任意时刻,软件或硬件复位都可以使系统初始化。软件复位是通过向配置寄存器的RS位写入逻辑1来实现的,复位后该位自动恢复为逻辑0。硬件复位是通过强制拉低RESET引脚50ns以上来实现。

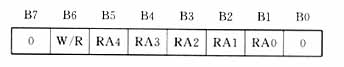

寄存器读写命令如下:

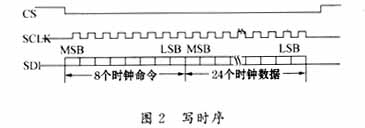

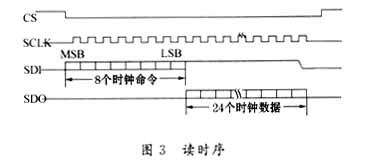

CS5460的串行接口部分集成了一个带有发送/接收缓冲器的状态机,状态机在SCLK上升沿解释8位命令字。根据对命令的解码,状态机将执行相应的操作,或者,为把寻址的内部寄存器的数据传送到发送缓冲区,写操作在数据传输前要等24个SCLK周期。通过寄存器读/写命令,数据可被写入或从CS5460A中读出,图2、图3为读、写时序。数据的读、写通过向串口SDI引脚写入相应的8位命令字(高位在前)来启动。需要注意的是:一些命令字在执行时受周期计数寄存器和配置寄存器内容的影响,需要先对周期计数器和配置寄存器内容进行正确设置。寄存器写指令后必须跟24位数据,先写命令字启动写操作,然后随着24个连续的串行时钟脉冲,CS5460A将从串行输入引脚SDI接收串行数据,一旦收到数据,状态机便将数据写入配置寄存器并返回到命令模式。寄存器读指令可以终止在8位的边界上。通过SDI引脚写入命令后,可从SDO引脚读出数据。

4 应 用

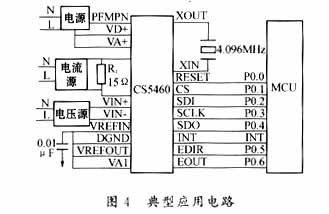

因为CS5460A可以用来测量瞬时电流、瞬时电压、瞬时功率、电能以及电压和电流的有效值,测量结果将以24位有符号或无符号形式存储在内部寄存器中,所以可以用CS5460A设计单相多功能电能表。另外,CS5460还提供了电能计量脉冲输出端口EOUT和功率方向端口EDIR,可以方便地与步进电机计数器连接构成简单的电能表。当晶振频率为4.096MHz,分频比为1,且两个转换器的直流输入皆为最大值时,输出脉冲的频率与脉冲速度寄存器的频率相同。

图4所示为一个典型的电度表电路,它的基本电流有效值Ib=20A,相线电压有效值V=220V(50Hz),计量常数K=500imp/kWh,最大电流有效值为Imax=100A,最大电压有效值为Vmax=300V,差分电压输入和差分电流输入最大值为150mV,电阻R1调整差分电流输入值。

如果用CS5460A设计电子式三相多功能电能表,可以在A、B、C每一相用一片CS5460A,每片输入参数值都要符合CS5460A技术要求,通过MCU对三相的能量等各参数进行处理,用MCU发出脉冲,同时可以计量每一相的用电情况。利用3片CS5460A设计的电子式三相多功能电能表,有功精度可达0.5级,无功精度可达1.0级,此表现已投入生产使用。

5 结束语

CS5460A性能优于其它单相计量芯片。目前,供电部门对电网的用电考核参数越来越多,如:有功、无功、瞬时电压、瞬时电流、瞬时功率等。而CS5460A提供了许多计量参数,设计在电能表中,其功能基本满足供电部门需求,市场前景极为广阔。