化学机械抛光(CMP)工艺由IBM于1984年引入集成电路制造工业,并首先用在后道工艺的金属间绝缘介质(IMD)的平坦化, 然后通过设备和工艺的改进用于钨(W)的平坦化, 随后用于浅沟槽隔离(STI) 和铜(Cu)的平坦化。化学机械抛光(CMP)为近年来IC制程中成长最快、最受重视的一项技术。其主要原因是由于超大规模集成电路随着线宽不断细小化而产生对平坦化的强烈需求。本文重点介绍CMP在集成电路中的非金属材料的平坦化应用。

集成电路工艺发展对平坦化的要求

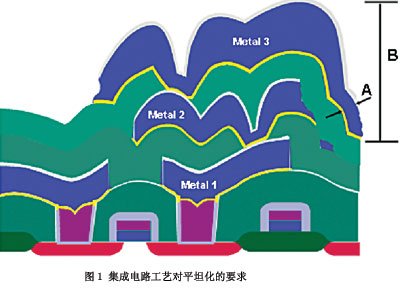

由于IC产业的快速发展,加上线宽的进一步缩小,使得晶片表面的高低起伏严重影响了制程技术的可靠性。以图1为例,由于表面层的高低起伏,所以我们每沉积一层薄膜,会使得表面的起伏变得更大,这种情况一直积累上去,到表面金属层时,在制程上会发生两个大问题:在镀上金属膜时,凹陷下去的部分和其它地方的厚度不均匀,如图中A处,此处不仅会引起电阻值增高,同时容易因为电子迁移而造成线路断路,造成元件具有很差的可靠性。另一方面,如果在这种凸凹不平的表面上涂覆光阻,在光阻显影时,会因为光阻深度不一,造成用来显影的光线在聚焦时,无法得到良好的解析度。通常线宽越窄,对解析度的要求越高,便需要提供愈短的距离来聚焦,这个距离称为聚焦深度,图中的B即代表此部分的元件的聚焦深度。

在CMP平坦工艺出现之前,集成电路工艺常用的平坦化方法包括:热流法(Thermal flow)、旋涂式玻璃法(Spin on Glass)、回蚀法(Etch Back)、电子环绕式共振法(Electron Cyclotron Resonance)。而CMP是唯一能够提供晶片全域性的平坦化,也就是说它能够将整个晶片上的高低起伏全部磨成理想的厚度,这是上述其它工艺方法所不能达到的,通过它们只能获得局部平坦化。这也是目前许多半导体厂在他们的制程中大量采用CMP抛光法的最大原因。

什么是CMP工艺

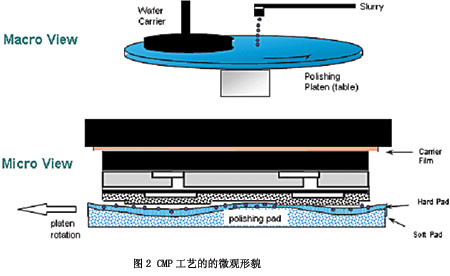

简单而言,CMP抛光工艺就是在无尘室的大气环境中,利用机械力对晶片表面作用,在表面薄膜层产生断裂腐蚀的动力,而这部分必须籍由研磨液中的化学物质通过反应来增加其蚀刻的效率。而研磨液、晶圆与研磨垫之间的相互作用,便是CMP中发生反应的焦点,如图2所示。CMP制程中最重要的两大组件便是浆料和研磨垫。浆料通常是将一些很细的氧化物粉末(粒径大约在50(m)分散在水溶液中而制成。研磨垫大多是使用发泡式的多孔聚亚安酯制成。在CMP制程中,我们先让浆料填充在研磨垫的空隙中,并提供了高转速的条件,让晶圆在高速旋转下和研磨垫与研磨液中的粉粒作用,同时控制下压的压力等其它参数。

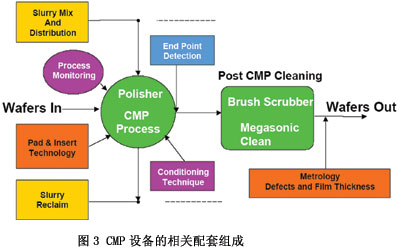

图3完整给出了CMP工艺相关的设备组成。可以看出,CMP的组成设备分为两部分,即研磨部分和清洗部分。研磨部分由四部分组成,即研磨液的引入和循环;研磨过程的监控;研磨耗材以及研磨运动组件。而清洗部分负责晶圆的清洗和甩干,做到“Dry in-Dry out”。

化学机械抛光的主要检测参数包括: 磨除速率(Removal Rate), 研磨均匀性(Uniformity)以及缺陷量 (Defect)。研磨速率是指给定时间内磨除的厚度总量,这种测试通常在控片上进行;研磨均匀性又分为晶圆内均匀性 (WIW NU)和晶圆间均匀性 (WTW NU)。晶圆内研磨均匀性指某片晶圆表面研磨速率的标准偏差;晶圆间研磨均匀性用于表征一定时间内晶圆表面材料研磨速率的连贯性。对于化学机械抛光而言,主要的缺陷种类包括表面小颗粒、表面刮伤、研磨剂残留等。它们将直接影响产品的良率。

CMP在非金属平坦化中的应用

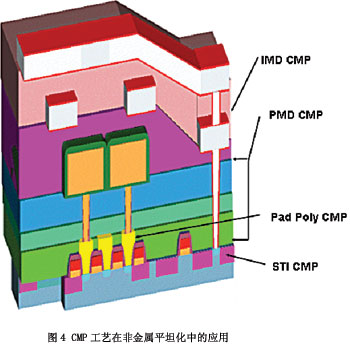

图4示出了CMP在集成电路制造工艺的非金属平坦化中应用,其中包括 STICMP, PolyCMP, PMDCMP 和IMDCMP。

A.浅沟槽隔离平坦化 (STI CMP)

STI目前已成为器件之间隔离的关键技术,目前已取代LOCOS(硅的局部氧化)技术。其主要步骤包括在纯硅片上刻蚀浅沟槽、进行二氧化硅沉积、最后用CMP技术进行表面平坦化。

STICMP的工艺目标是磨掉比SiN层高的所有氧化层,否则STI抛光后进行的工艺就不能用热磷酸剥离掉SiN,从而实现平坦化。在抛光过程中,SiN被用作抛光阻挡层,通过终点检测当研磨从氧化硅过渡到氮化硅的时候停止抛光过程。另外,氮化硅的厚度也决定了允许的CMP过抛光量,并使抛光过程不至于把器件的有源区暴露并带来损伤。 STI抛光工艺的难点之一是避免沟槽中的氧化硅减薄太多,或产生凹陷。这种情况是由于抛光垫使得在压力的作用下,在宽的沟槽区产生缺陷。

B. 多晶硅平坦化 (Poly CMP)

多晶硅层广泛用于DRAM器件制造中的电容结构、门(gate)结构或者多晶硅塞(Plug)等。而PolyCMP工艺目前已广泛应用在生产实际中。对于 Poly CMP而言,保证研磨速率的一致性和可重复性至关重要。早期的PolyCMP工艺的弱点就是较难达到这个良好的研磨速率,研磨后晶圆表面的平整度不稳定。这主要是因为这些工艺侧重于利用研磨液的化学作用以磨去多晶硅。殊不知,在这类研磨液作用下,多晶硅表面被反应生成氧化物并因此阻碍硅表面研磨的继续进行。研磨终点的精确控制也是PolyCMP 的重点。否则,对晶圆的过度研磨使得门区域(Gate)、塞子(Plug)中的多晶硅严重磨损,这会影响将来器件的性能,因为它有可能改变器件中掺杂结构的电性能

C.层间介质平坦化(PMD CMP)

ILD 为实际器件提供IMD层的金属连线的绝缘层,ILD氧化层包括一层薄氮化硅或氮氧化硅,用做器件保护层和金属连线的阻挡层,其上面是一层用等离子增强工艺或高密度等离子体工艺淀积的厚掺杂氧化硅层。

D.金属间介质平坦化 (IMD CMP)

淀积在金属层之间的层间介质(IMD)用来对金属导体进行电绝缘。它通常是高密度等离子体CVD淀积后,紧接着进行PECVD淀积。这是因为HDPCVD氧化层具有优良的细缝隙填充特性,而PECVD可以提高产量和降低成本。氧化层用CMP抛光至特定厚度,不需要抛光停止层。